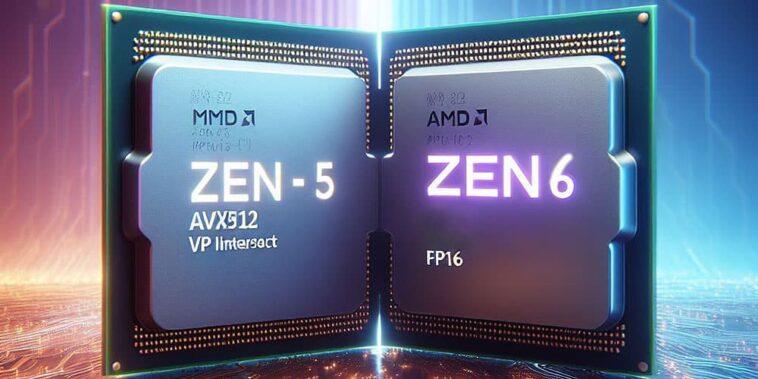

AMD est un pas en retard sur Intel en matière d’IA dans tous les aspects. En fait, Intel a une avance très importante en unissant ses CPU et GPU contre les options d’AMD, et ils constituent le principal atout pour contrer la poussée de NVIDIA. Gaudi2 est actuellement meilleur en termes de performances/prix, tandis que les Xeons sont omniprésents sur le marché des serveurs IA, et évidemment, AMD ne peut pas laisser cela se produire. Par conséquent, les processeurs Zen 5 et Zen 6 disposeront de nouveaux supports d’instructions AVX512 pour les calculs d’inférence complexes, c’est-à-dire l’IA. Pour être précis, Zen 5 prend en charge AVX512-VP2INTERSECT et Zen 6 AVX512-FP16.

En fait, les informations sont un peu plus larges et Cela ne se limite pas exclusivement à ces instructions, même s’il n’y a que des coups de pinceau. Pour résumer l’idée, l’objectif d’AMD est de former un écosystème de style Intel, où il continuera à échouer dans quelque chose de clé comme la pile logicielle, mais en termes de matériel, il semble que ce sera plus proche cette fois.

AMD Zen 5, prise en charge de quatre nouvelles instructions, dont AVX512-VP2INTERSECT

Hay que ser específicos a la hora de hablar de lo filtrado, y aunque no vamos a cubrir todas las instrucciones al completo porque daría para artículos independientes, sí que tocaremos brevemente algunas por encima: En concreto, las instrucciones que soportará Zen 5 como novedades son les suivantes:

- AVX-VNNI

- MOVDIRI/MOVDIR64B

- AVX512_VP2INTERSECT

- PRÉFETCHI

Les plus importants sont peut-être le premier et le troisième, dont nous avons déjà discuté à d’autres occasions et que nous reviendrons. AVX-VNNI (Vector Neural Network Instructions) est une extension x86 faisant partie d’AVX512 au sein de sa branche Foundation.

Il s’agit d’une instruction axée sur l’accélération des algorithmes de réseaux neuronaux convolutifs et divisée en quatre sous-instructions. Intel commente dans ses fiches techniques que ces réseaux nécessitent la multiplication requise de deux valeurs de 16 bits ou de deux valeurs de 8 bits, et que celles-ci accumulent le résultat en une valeur de 32 bits. Cependant, ils prennent en charge les valeurs 128 bits et 256 bits et ont été mis en service à Cascade Lake en 2019. De plus, Zen 4 les prend déjà en charge, ils faciliteront donc ces calculs et seront pris en charge par AVX512-VP2INTERSECT.

Sachant que Zen 5 les prendra également en charge, AVX512-VP2INTERSECT résoudra un autre problème supplémentaire. Cette instruction a une fonction simple à comprendre et complexe à exécuter, puisqu’elle va calculer l’intersection entre les DWORDS et les QUADWORDS, ainsi que les registres de masques.

MOTS et Opcode par instruction

Les deux MOTS sont essentiellement des unités de données complexes qui font deux fois la taille d’un mot (DWORDS) ou quatre fois la taille d’un mot (QUADWORDS). En comprenant cela, nous savons sûrement ce qu’est un MOT en tant que tel, mais pour ceux qui ne le savent pas, il est défini comme une chaîne de bits avec une taille et une longueur spécifiques qui, logiquement, font référence au nombre de bits qu’elle contient.

Sachant cela, Intel définit l’instruction AVX512-VP2INTERSECT dans sa fiche technique de jeu d’instructions comme une instruction réelle qui écrit une paire de registres de masque pair/impair. De même, la destination de l’enregistrement de masque indiquée dans le champ MODRM.REG est utilisée pour former la base de la paire d’enregistrements. Le bit sous ce champ est masqué (mis à zéro) pour créer le premier enregistrement de la paire, mais EVEX.aaa et EVEX.z doivent être nuls.

A terme, cette instruction accélérera le calcul des intersections entre DWORDS et QUADWORDS pour accélérer les tâches d’inférence complexes destinées au DL et à l’IA.

AMD Zen 6, l’étape définitive vers l’écosystème CPU+GPU pour l’IA grâce à AVX512-FP16

Actuellement, Zen 4 prend en charge dans l’EPYC pour BF16, mais pas pour FP16. Zen 5 ne semble pas non plus avoir de support, et Intel a ici un avantage très significatif, et il y est parvenu en deux étapes très curieuses. L’AVX512-FP16 a fait ses débuts en 2020 avec Cooper Lake, mais Intel a laissé là la prise en charge de ses deux architectures suivantes, car elles ne l’incluaient pas.

Dans la même année 2020 est sorti Tiger Lake, qui n’offrait évidemment pas de support, et en 2021 Rocket Lake a fait exactement la même chose, principalement parce que ce n’était pas nécessaire sur le bureau puisqu’il n’y avait pas de NPU en tant que tel. Mais ensuite, en 2021, Alder Lake lui-même est arrivé et les a de nouveau soutenus.

Ice Lake sur les serveurs ne l’a pas reçu (pour le moins curieux) et plus tard, avec Sapphire Rapids l’année dernière, il a été étendu à l’AMX-FP16, et pas seulement à l’AVX512-FP16. Avec cela, un serveur essaie de laisser entendre qu’Intel n’a pas eu la tâche facile ni n’a simplement convaincu le marché, puisqu’au début personne ne soutenait cette instruction.

Mais Zen 6 supportera cet AVX512-FP16, on comprend qu’à un moment donné en 2025, probablement fin 2025 si tout se passe comme prévu, mais à quoi AMD va-t-il les utiliser ? Eh bien, pour la même raison qu’Intel les utilise actuellement, où il a un avantage très clair : accélérer l’inférence par rapport au FP32.

Jusqu’en 2025 ou 2026 nous ne verrons pas AMD rivaliser pleinement avec ses CPU en IA, la solution temporaire ? Un NPU plus rapide

Là encore, il faut revenir à la fiche technique d’Intel, où ils expliquent comment ils abordent les avantages de l’AVX512-FP16 :

Les formats FP16 et INT8, qui sont des formats de poids compressés où ils sont compressés pour avoir une taille plus petite. L’inconvénient de ces compressions est la précision du modèle ou encore appelée erreur de quantification.

Plus il y a de bits alloués pour représenter les données, plus la plage qu’ils peuvent représenter est grande et potentiellement meilleure la précision du modèle. Cependant, des données plus volumineuses nécessitent plus d’espace mémoire à stocker, plus de bande passante mémoire nécessaire pour les transférer, ainsi que plus de ressources informatiques et de temps d’utilisation.

Par conséquent, avec ces informations divulguées, nous pouvons conclure qu’AMD sera en concurrence dans l’IA tant sur les serveurs que sur les PC et les ordinateurs portables de manière beaucoup plus puissante dès cette année, mais surtout avec des vues tournées vers 2025, puisqu’ici elle va avec un peu de retard par rapport à Intel, il compense donc une grande partie du déficit avec ses NPU.